## Prediction and Management of Point Defects for Improved Performance of PV Semiconductors (PV-4)

A joint India-U.S. research consortium funded under the Joint Clean Energy Research & Development Center (JCERDC)

## Scientific Achievement:

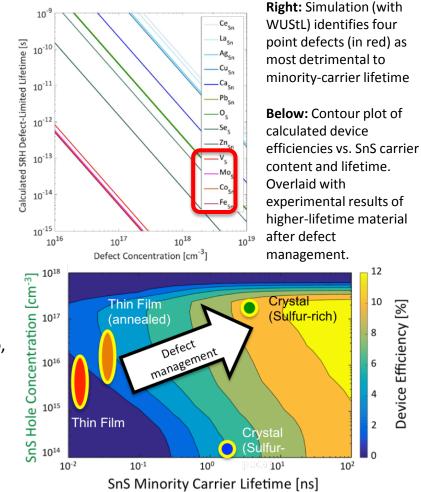

A DFT / SRH model run in collaboration with WUStL<sup>[1]</sup> identified the most detrimental defects to carrier lifetime in SnS. Carrier lifetimes improved from <100 ps <sup>[2]</sup> in thin films to >3 ns<sup>[3]</sup> in bulk crystals with targeted defect engineering.

## Significance and Impact:

Device modeling<sup>[4]</sup> indicates that achieving >1 ns carrier lifetimes in SnS would enable 10+%-efficient devices. We have achieved >3 ns lifetimes in SnS crystals, and are attempting to translate this success to thin films for improved device performance.

## **Research Details:**

SERI IUS

- DFT / SRH model identifies four most detrimental defects: V<sub>s</sub>, Mo<sub>sn</sub>, Co<sub>sn</sub>, and Fe<sub>sn</sub>

- Crystal samples grown from feedstocks containing <1 ppb Mo, Co, and Fe

- Crystals grown with S/Sn ratios ranging from 48/52 to 52/48

- Crystals grown with slow (5-day) linear cool-down from melt

- S-rich crystals exhibit improved lifetime (>3 ns) over S-poor crystals (~2 ns), but both show great increases over films (<100 ps)

Publication(s): [1] Polizzotti et al., IEEE PVSC (2016); [2] Jaramillo, R. et al., J. Appl. Phys. 119, 035101 (2016); [3] Polizzotti et al., MRS Fall (2016); [4] Mangan, N. M. et al. IEEE PVSC (2014).

Contact(s): Alex Polizzotti (a zotti@mit.edu) and Prof. Tonio Buonassisi (buonassisi@mit.edu)

Device Efficiency [%]